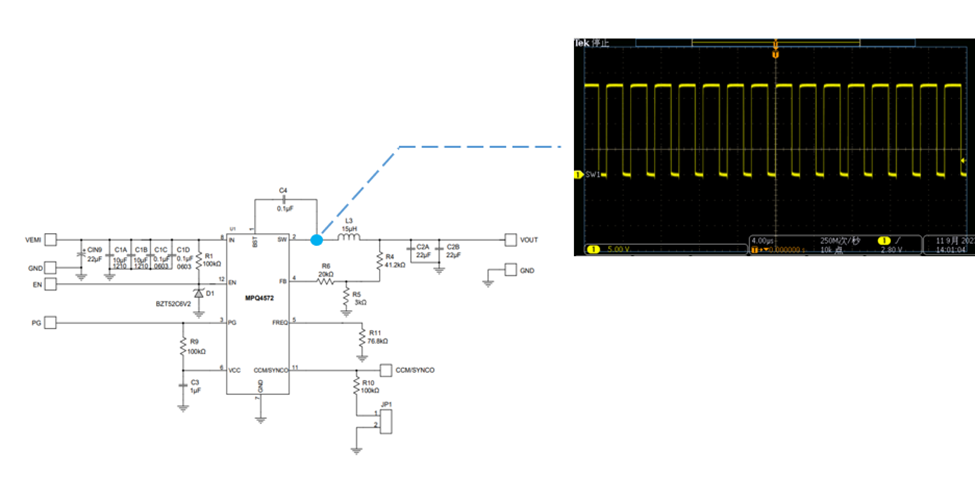

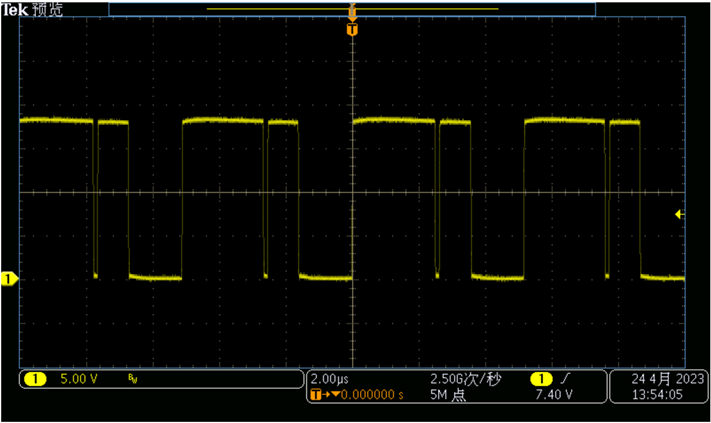

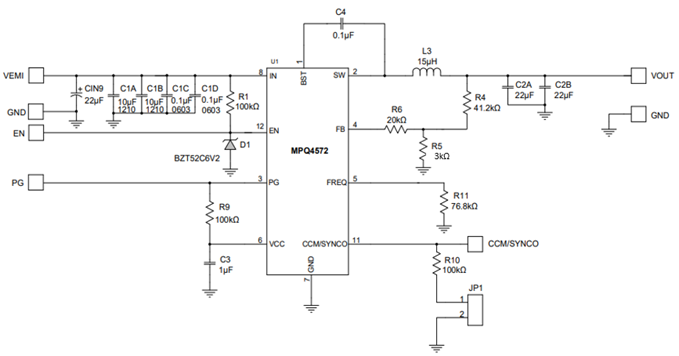

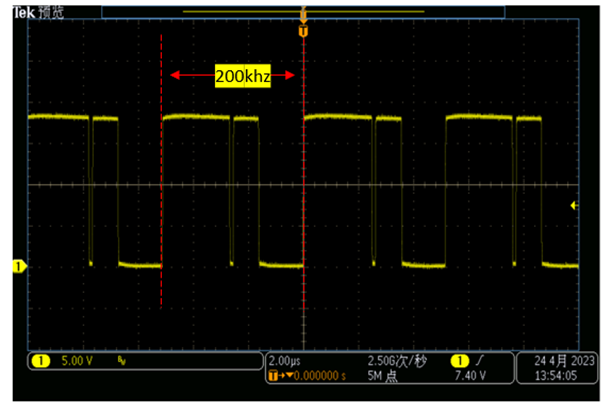

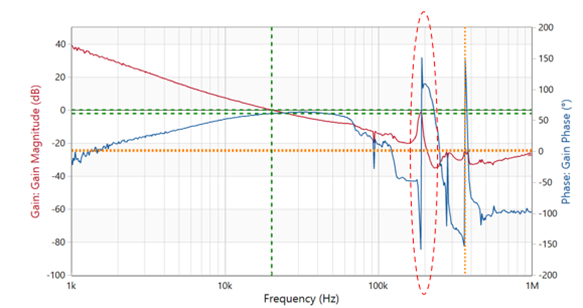

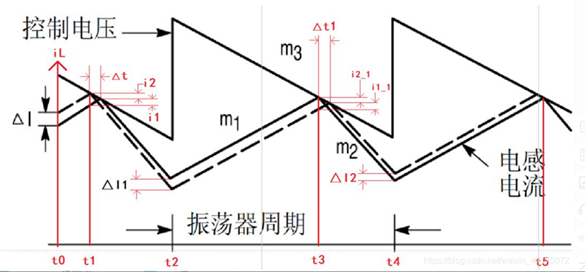

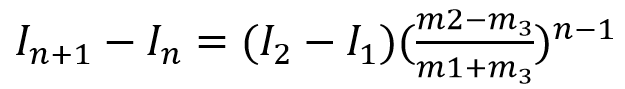

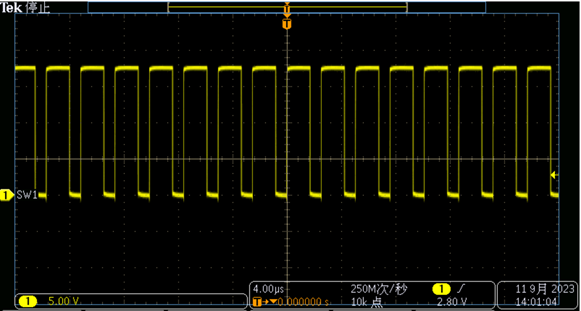

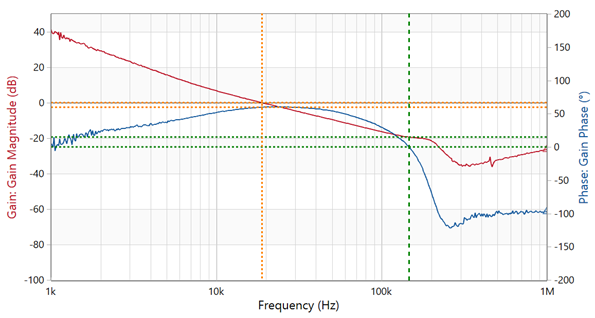

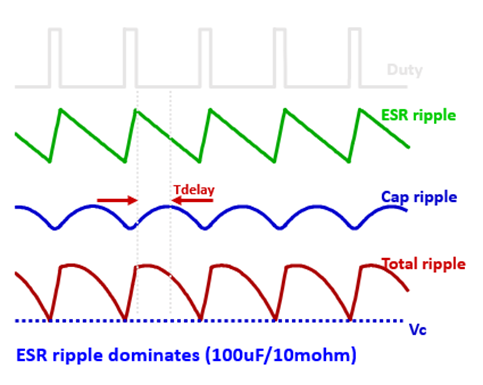

大家在测试电源电路时,有时会碰到输出电压异常、输出纹波过大等情况,此时通常会排查 SW SW 代表 BUCK 电路中的开关节点。在标准工作条件下,SW 点的波形表现为固定频率的方波。 然而,在某些不正常的情况下,SW 波形会呈现大小波状态。通常伴随着输出电压不稳定、效率降低、芯片异常发热,以及噪声纹波增大等问题。 因此,在开关电源设计中,常常要采取一定的措施来控制 SW 节点上的电压波动,以确保电源的稳定性和可靠性。 本文将从原理图设计和PCB 设计两个方面,分析 SW 出现大小波的原因,并介绍对应的解决办法。 是一款支持 4.5V 到 60V 的宽输入电压范围,持续输出电流 2A,采用峰值电流控制模式的降压芯片。 测试当前的环路波形,根据 bode 图能够正常的看到在 200khz 时,增益曲线出现尖峰,相位曲线翻转,能判断是发生了次谐波振荡。当输入电压升高到 25V 以上时,SW 波形恢复正常。 已知在峰值电流模式下,当占空比大于 50% 时,系统可能会变得不稳定,出现次谐波振荡,SW 呈现大小波。 为了保证电路工作稳定,要让扰动量收敛。注入的斜坡斜率 m3 要大于 0.5 倍 m2 才能使该式收敛。如果 m3 小于 0.5 倍 m2,即使注入了斜坡信号,也没有办法解决次谐波振荡问题。 芯片内部注入的斜坡信号斜率通常是未知的固定值,也就是说 m3 是固定的,那么我们大家可以通过增加电感感量减小 m2 来保证 m3>0.5 倍 m2 成立。当电感感量由 15uh 修改为 33uh 后,SW 波形恢复正常。 测试此时的 bode 图,200khz 时的增益曲线尖峰消失,环路稳定。 COT 是通过比较Vref 与 FB 管脚的电压来实现恒压控制,理想的 FB 电压与电感电流同相位。FB 采样的输出电压纹波信号由电容 ESR 越大,总的电路相位延迟越小,纹波接近线性,可以有效抑制次谐波振荡。 当为了效率及输出纹波幅度考虑,需要选择 ESR 比较小的电容时,我们可以选择注入斜坡补偿。通过外部的 RC 补偿给 FB 管脚注入斜坡信号,由Rs 至关重要。在 COT 控制模式下,当输出纹波由 ESR 主导时,电路稳定;由电容纹波主导时,可能出现次谐波振荡。此时,我们能够最终靠选用 ESR 较大的电容、 声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。举报投诉电源电路 技术案例笔记 / 除了跟设计工艺有关之外,还与绝缘表面的清洁、干燥程度、引线长度、引线截面积 避免产品整体研发完成后才交付 EMI 实验室进行测试 EMI 预兼容测试:在最早的时间 应用案例 / hierarchy partition后,为何maia_cpu做floorplan时候不见pin? partition是否将pin push下去,我们大家可以debug一下,回到maia_topdown/work目录下,invs打开MAIA命令如下: 脑电图(Electroencephalography,EEG)的奠基。脑电图显示了脑内电波的活动,开启了对大脑功能状态的研究新纪元。阿尔法 怎么接呀,看硬件设计手册说,reset不接,悬空,swdio和swclk接100K上拉。但是看EVAL板是接了reset,swdio,swclk,并且都是直连,没有上下 2505H成功获得了融合快充功能认证证书,证书编号10R0M-UFCS00075。此款产品是继智融 2325通过UFCS融合快充功能认证 / 使用AD5546做精密衰减的参考电路,有一个反馈电容C6,这个电容值的 在使用AD5546做精密衰减的参考电路中,有一个反馈电容C6。这个电容值的 OOM异常,需要经过以下几个步骤: 理解OOM异常的原因:OOM异常通常有以下几个原因:内存泄露、内存溢出、内存不足以容纳所需的数据等。理解OOM异常的原因对 问题很重要。 配置Java堆内存:要解决OOM异常,能够尝试增加Java堆内存的 有两台样机使用AD7708,相同程序,一台正常。另一台AD转换速度有时候正常,有时候特别满。用示波器查看ready引脚信号,也能 串口通信问题? / 的就是高速,一涉及到高速板有些人就比较茫然。高速板主要考虑两个问题点,当然其它3W,2H是基本点。 驱动LSM6DS3TR-C实现高效运动检测与数据采集(10)----融合磁力计进行姿态解算 2024年上海海思MCU开发者体验官招募,手机/MatePad大奖等你拿! HarmonyOS Next原生应用开发-从TS到ArkTS的适配规则(十一)